研修室ブログ

日々スキルアップや自己研鑽に励む社員や、それをサポートする講師・間接部門スタッフがその日常をつづります。

- ハードウェア言語(HDL)について

-

2017年6月14日(水)

組込み系エンジニアのT.Mです。

HDL(HardWare Description Language)をご存知でしょうか。ハードウェア言語と呼ばれ、「VerilogHDL」「SystemC」があります。

ハードウェア設計とは電気系の人が主にする作業で、回路を設計し、回路図を元に物を作成をします。よって、物が出来て初めて動作等の確認を行うことになります。その物を使用して、組込み系エンジニアはプログラムを組んで実行に移します。

この段階では、ハードで問題があっても設計しなおすことは出来ないので、組込み系エンジニアが辻褄あわせでプログラムを組むことになります。 その辺りがわからないまま上流工程で設計されてしまい、組込み系エンジニアが苦労し、最終的には納期が延びるということになってしまいます。

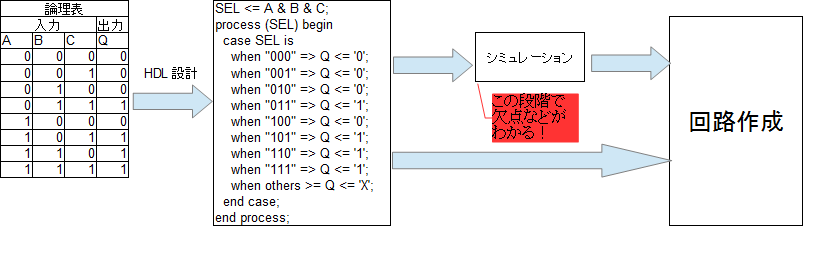

HDLでは回路設計~チップの作成(実際は物ではなくシミュレーション上)までを全てプログラム言語で実装をする事が出来ます。たとえば、回路図でAND回路、OR回路などを書くと、真理表を見ないと入出力がイメージできません。結局は物を作らないことにはわからないのです。

しかし、HDLを使用すると、回路をプログラムで記述することになるため、明示的に記述することができます。 また、作成したプログラムをバーチャル上で動かせるため、実際に基盤を組み立てる前の段階で動作等の確認が可能です。

結果、上流設計の時点で不具合などを見つけやすくなり、不具合を直した状態での基盤作成になるので、手戻りが少なくなる利点があります。こうして設計の最初の段階で不具合を見つけることにより、開発期間の短縮が可能になるため、最終的にはコストダウンにもなります。

SystemC言語は約20年ぐらい前に開発されたのですが、C++ベースです。 組込み系エンジニアがハードウェアエンジニアになるのはハードルが高いですが、C++を使用したことがある人は入りやすいと思います。

これを機にハードウェアエンジニアを目指してみてはいかがでしょうか?ハード、ソフト、両方出来る人はあまりいないため、重宝されると思いますよ。 筆者:T.M(組込み系エンジニア)

タグ:組込み系